## Novoptel

# Polarization scrambler/transformer module EPS1000

#### **Revision history**

| Version | Date       | Remarks                           | Author          |  |  |

|---------|------------|-----------------------------------|-----------------|--|--|

| 0.9.7   | 13.08.2013 | Draft version                     | R. Noé, B. Koch |  |  |

| 0.9.8   | 01.08.2014 | Extended SPI register description | B. Koch         |  |  |

#### **General description**

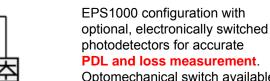

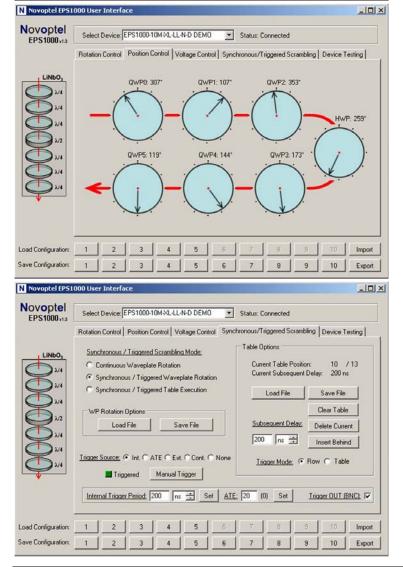

The EPS1000 polarization scrambler/transformer modules comprises miniaturized, ultrafast, low-power optical polarization transformers (without feedback). They can be configured for a variety of purposes, namely polarization scrambling with rotating optical waveplates and the triggered or repetitive execution of a sequence of optical waveplate or driving voltage settings.

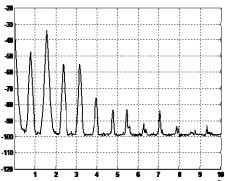

A daughterboard is available for optical power measurement (options O and OO). Simultaneous to the polarization transformer settings, optical intensities can thus be measured. This is useful for calibrated PDL measurements. Other components such as optical switches, digitally controlled variable optical attenuators and tap couplers can likewise be included.

The module runs from a single +5V supply. No logical connections are needed, nor any programming via JTAG port. For increased functionality, a few hard-wired logical lines are provided. Parameters may be set and read by two serial interfaces, SPI and UART. This accesses the full EPS1000 functionality. In a commercial test and measurement environment it is also recommended to connect the JTAG port, in order to allow firmware upgrades. In the desktop unit, the UART of the module is replaced by USB.

#### **Ordering information**

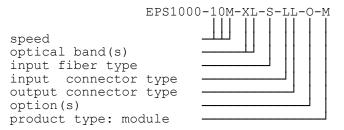

For example, the type EPS1000-10M-XL-S-LL-O-M can scramble polarization at up to 10 Mrad/s (20 Mrad/s with reduced accuracy), works from optical C to L band, has standard fiber at the optical input, has LC/UPC connectors and includes the option of optical power measurement.

Novoptel GmbH EIM-E Warburger Str. 100 33098 Paderborn Germany www.novoptel.com

Novoptel reserves the right to change module and specifications.

#### Absolute maximum ratings

| Parameter                       | Value      | Remarks/Conditions |

|---------------------------------|------------|--------------------|

| Supply voltage                  | –0.3+5.5 V |                    |

| Voltage at all logical ports    | –0.3+3.6 V |                    |

| Optical input power at any port | +20 dBm    |                    |

| Storage temperature             | –40+85°C   |                    |

| Operating temperature           | −10+70°C   |                    |

### Characteristics

| Parameter                       | Value              | Remarks/Conditions                               |

|---------------------------------|--------------------|--------------------------------------------------|

| Wavelength range                | 15291562 nm        | C = optical C band                               |

| (covered if letter is included  | 15291568 nm        | X = extended optical C band                      |

| in part number)                 | 15681610 nm        | L = optical L band. 1625 nm upper limit is under |

|                                 |                    | consideration.                                   |

|                                 | tbd1529 nm         | S = optical S band                               |

|                                 | 1310 nm            | 3 = optical 1310 nm band (range tbd)             |

| Optical input power for optical | –11 dBm or tbd     | Only valid with options O and OO. The            |

| power measurement               |                    | scrambler input power is independent of this.    |

| Optical insertion loss          | 1.53 dB            | From optical scrambler input to optical output.  |

|                                 | (typically 2.5 dB) |                                                  |

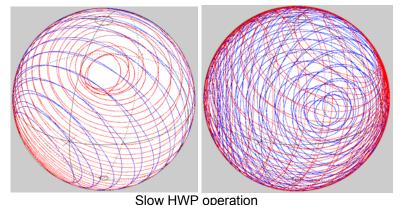

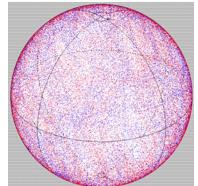

| Maximum polarization            | 10 Mrad/s or tbd   | Scrambling at up to 20 Mrad/s is possible with   |

| scrambling speed of halfwave    |                    | reduced accuracy. Speed may be reduced at        |

| plate (HWP)                     |                    | corners of operating temperature range.          |

| Maximum polarization            | 1 Mrad/s or tbd    |                                                  |

| scrambling speed of             |                    |                                                  |

| quarterwave plates (QWPs)       |                    |                                                  |

| Supply voltage                  | +4.755.25 V        |                                                  |

| Supply current                  | 1.41.7 A or tbd    | For 10 Mrad/s version at low scrambling          |

|                                 |                    | speeds.                                          |

|                                 | 2.12.5 A or tbd    | For 10 Mrad/s version operated at 20 Mrad/s.     |

|                                 |                    | Versions with reduced maximum polarization       |

|                                 |                    | scrambling speed and supply current are also     |

|                                 |                    | available.                                       |

| Logical port levels             | LVCMOS33           | 3.3 V CMOS logic                                 |

## Type of optical input

| Туре | Function                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S    | Standard singlemode fiber. Standard version.                                                                                                                     |

| Р    | Polarization-maintaining fiber (PANDA). This may be useful in scenarios where an optical source with polarization-maintaining fiber is connected to the EPS1000. |

#### **Connector types**

| Туре       | Function                                                                         |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| N          | none                                                                             |  |  |  |  |  |

| F          | FC/UPC                                                                           |  |  |  |  |  |

| Α          | FC/APC                                                                           |  |  |  |  |  |

| L          | LC/UPC                                                                           |  |  |  |  |  |

| S          | SC/PC                                                                            |  |  |  |  |  |

| E          | E2000                                                                            |  |  |  |  |  |

| Eirot lott | at latter aposition input connector, accord latter aposition output connector(a) |  |  |  |  |  |

First letter specifies input connector, second letter specifies output connector(s).

## Options

| Туре | Function                                                                                  |

|------|-------------------------------------------------------------------------------------------|

| 0    | Optical power measurement. Simultaneous to the polarization transformer settings, optical |

|      | intensities can thus be measured. A back-to-back measurement permits one to determine     |

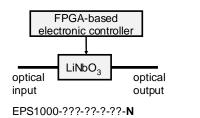

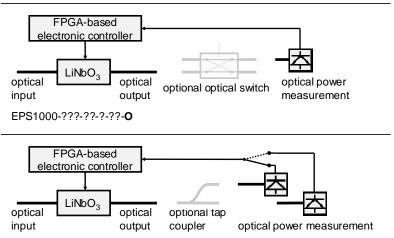

the polarization-dependent loss of the EPS1000. Subsequently, calibrated PDL (or simply loss) measurements of a device under test are possible. The optical power range can be increased by different input attenuations, to be set by a variable attenuator or the insertion of a fixed attenuator. An optical switch can also be included in the desktop version. 00 Like option O, but 2 optical inputs are provided, selectable by a fast electronic switch. This allows for ratiometric measurements without optical reconfiguration. A tap coupler can also be included and spliced. Ν None. Space is available for a small daughterboard, the connections of which are detailed upon request. More digital inputs/outputs and analog inputs are available on the EPS1000 module. This means that other components such as digitally controlled variable optical attenuators and optical switches can be connected and operated by the user. One example is a variable optical attenuator at the input of an EPS1000 with option O, which increases the dynamic range of loss measurement. Details upon request.

EPS1000-???-??-??-**OO**

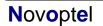

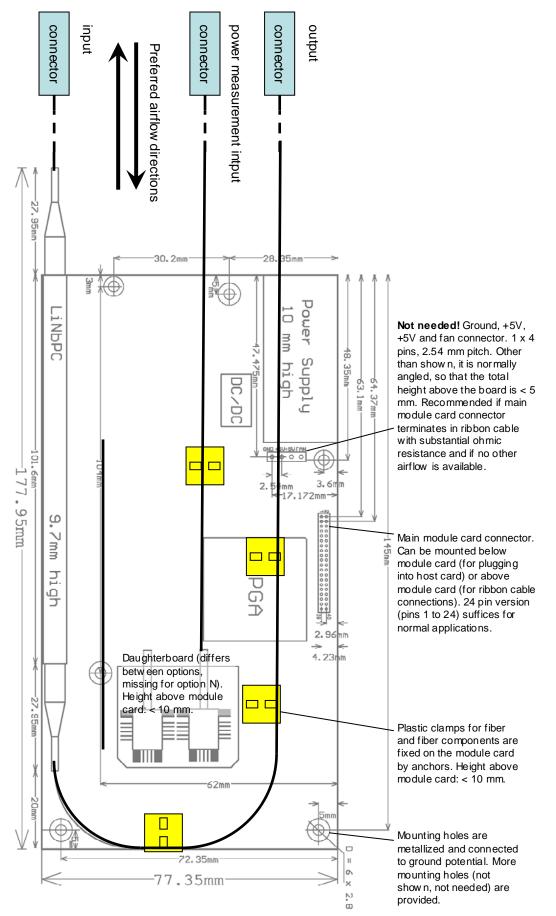

Fig. 1: Simplified block diagram for various configurations, and associated ordering codes

#### **Electrical connector**

| Nr.  | Name  | I/O | Logic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INI. |       |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1    | RE1   | I/O | LVCMOS33 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2    | URXD  | I/O | LVCMOS33 | UART RXD. For parameter setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3    | ABS   | 0   | LVCMOS33 | Module Absent. High level "1" is module absent, low level (0) is<br>module present. Pull-up resistor (e.g., 10 kOhm to +3.3 V) on host<br>card is therefore needed (3). On the module ABS will be connected<br>to an FPGA output that is permanently set to low level "0". (Note:<br>Therefore, during reset, the FPGA output will have high impedance<br>and the pull-up resistor on the host card will pull ABS high "1" for a<br>short time. It would be more logical to provide a galvanic connection<br>of ABS to ground in the module. But the chosen solution is more<br>versatile, because ABS could be re-programmed to get another<br>function (like RE1RE8).) |

| 4    | +5V   |     |          | +5 V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5    | SDO   | 0   | LVCMOS33 | SPI Data Out. For parameter setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6    | +5V   |     |          | +5 V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7    | +3.3V |     |          | +3.3 V. Can be used to power an external JTAG cable. Do not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |       |     |          | apply externally generated voltage here. (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Novoptel**

| 9         RE3         I/O         LVCMOS33         Reserved (2)           10         TCK         I         LVCMOS33         JTAG. For firmware upgrade.           11         RE4         I/O         LVCMOS33         Reserved (2)           12         TMS         I         LVCMOS33         SPI Enable. For parameter setting.           13         CS         I         LVCMOS33         SPI Enable. For parameter setting.           14         TDI         I         LVCMOS33         Reserved (2)           16         SDCK         I         LVCMOS33         Reserved (2)           16         SDCK         I         LVCMOS33         SPI Data Clock. For parameter setting.           17         GND          -         Ground           18         SDI         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND          -         Ground           21         GND         -         -         Ground           22         TRGIO         I/O         LVCMOS33         Reserved (2)           23         RE6         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O                                                                                                                  | 8  | RE2  | I/O | LVCMOS33 | Reserved (2)                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-----|----------|---------------------------------------------------------------|

| 10         TCK         I         LVCMOS33         JTAG. For firmware upgrade.           11         RE4         I/O         LVCMOS33         Reserved (2)           12         TMS         I         LVCMOS33         JTAG. For firmware upgrade.           13         CS         I         LVCMOS33         SPI Enable. For parameter setting.           14         TDI         I         LVCMOS33         SPI Enable. For parameter setting.           14         TDI         I         LVCMOS33         SPI Data Clock. For parameter setting.           16         SDCK         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND           Ground           20         TDO         O         LVCMOS33         SPI Data In. For parameter setting.           21         GND           Ground           22         TRGIO         I/O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33                                                                                        |    |      |     |          |                                                               |

| 11       RE4       I/O       LVCMOS33       Reserved (2)         12       TMS       I       LVCMOS33       JTAG. For firmware upgrade.         13       CS       I       LVCMOS33       SPI Enable. For parameter setting.         14       TDI       I       LVCMOS33       Reserved (2)         16       SDCK       I       LVCMOS33       SPI Data Clock. For parameter setting.         17       GND         Ground         18       SDI       I       LVCMOS33       JTAG. For firmware upgrade.         20       TDO       O       LVCMOS33       SPI Data Clock. For parameter setting.         19       GND         Ground         20       TDO       O       LVCMOS33       JTAG. For firmware upgrade.         21       GND         Ground         22       TRGIO       I/O       LVCMOS33       Trigger input/output in synchronous/triggered scrambling mode         23       RE6       I/O       LVCMOS33       Reserved (2)         24       RE7       I/O       LVCMOS33       Reserved (2)         25       UTXD       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                            | 10 |      | 1   |          |                                                               |

| 13         CS         I         LVCMOS33         SPI Enable. For parameter setting.           14         TDI         I         LVCMOS33         JTAG. For firmware upgrade.           15         RE5         I/O         LVCMOS33         Reserved (2)           16         SDCK         I         LVCMOS33         SPI Data Clock. For parameter setting.           17         GND          -         Ground           18         SDI         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND          -         Ground           20         TDO         O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30 <td>11</td> <td></td> <td>I/O</td> <td></td> <td></td>                                     | 11 |      | I/O |          |                                                               |

| 13         CS         I         LVCMOS33         SPI Enable. For parameter setting.           14         TDI         I         LVCMOS33         JTAG. For firmware upgrade.           15         RE5         I/O         LVCMOS33         Reserved (2)           16         SDCK         I         LVCMOS33         SPI Data Clock. For parameter setting.           17         GND          -         Ground           18         SDI         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND          -         Ground           20         TDO         O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30 <td>12</td> <td>TMS</td> <td>I</td> <td>LVCMOS33</td> <td>JTAG. For firmware upgrade.</td> | 12 | TMS  | I   | LVCMOS33 | JTAG. For firmware upgrade.                                   |

| 15         RE5         I/O         LVCMOS33         Reserved (2)           16         SDCK         I         LVCMOS33         SPI Data Clock. For parameter setting.           17         GND           Ground           18         SDI         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND           Ground           20         TDO         O         LVCMOS33         JTAG. For firmware upgrade.           21         GND           Ground           22         TRGIO         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           26         RE8         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30         RE12         I/O         LVCMOS33                                                                                                                                                                     | 13 | CS   | I   | LVCMOS33 | SPI Enable. For parameter setting.                            |

| 16       SDCK       I       LVCMOS33       SPI Data Clock. For parameter setting.         17       GND         Ground         18       SDI       I       LVCMOS33       SPI Data In. For parameter setting.         19       GND         Ground         20       TDO       O       LVCMOS33       JTAG. For firmware upgrade.         21       GND         Ground         22       TRGIO       I/O       LVCMOS33       Reserved (2)         23       RE6       I/O       LVCMOS33       Reserved (2)         24       RE7       I/O       LVCMOS33       Reserved (2)         25       UTXD       I/O       LVCMOS33       Reserved (2)         26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Res                                                                                                                                                                                                                               | 14 | TDI  |     | LVCMOS33 | JTAG. For firmware upgrade.                                   |

| 17       GND         Ground         18       SDI       I       LVCMOS33       SPI Data In. For parameter setting.         19       GND         Ground         20       TDO       O       LVCMOS33       JTAG. For firmware upgrade.         21       GND         Ground         22       TRGIO       I/O       LVCMOS33       Trigger input/output in synchronous/triggered scrambling mode         23       RE6       I/O       LVCMOS33       Reserved (2)         24       RE7       I/O       LVCMOS33       Reserved (2)         25       UTXD       I/O       LVCMOS33       Reserved (2)         26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LV                                                                                                                                                                                                                      | 15 | RE5  | I/O | LVCMOS33 |                                                               |

| 18         SDI         I         LVCMOS33         SPI Data In. For parameter setting.           19         GND           Ground           20         TDO         0         LVCMOS33         JTAG. For firmware upgrade.           21         GND           Ground           22         TRGIO         I/O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           26         RE8         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30         RE12         I/O         LVCMOS33         Reserved (2)           31         RE13         I/O         LVCMOS33         Reserved (2)           32         RE14 <td< td=""><td>16</td><td>SDCK</td><td></td><td>LVCMOS33</td><td>SPI Data Clock. For parameter setting.</td></td<>                    | 16 | SDCK |     | LVCMOS33 | SPI Data Clock. For parameter setting.                        |

| 19         GND          Ground           20         TDO         0         LVCMOS33         JTAG. For firmware upgrade.           21         GND          Ground           22         TRGIO         I/O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           26         RE8         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30         RE12         I/O         LVCMOS33         Reserved (2)           31         RE13         I/O         LVCMOS33         Reserved (2)           32         RE14         I/O         LVCMOS33         Reserved (2)           33         RE15         I/O         LVCMOS33         Reserved (2)                                                                                                           | 17 | GND  | 1   |          |                                                               |

| 20TDOOLVCMOS33JTAG. For firmware upgrade.21GNDGround22TRGIOI/OLVCMOS33Trigger input/output in synchronous/triggered scrambling mode23RE6I/OLVCMOS33Reserved (2)24RE7I/OLVCMOS33Reserved (2)25UTXDI/OLVCMOS33UART TXD. For parameter setting.26RE8I/OLVCMOS33Reserved (2)27RE9I/OLVCMOS33Reserved (2)28RE10I/OLVCMOS33Reserved (2)29RE11I/OLVCMOS33Reserved (2)30RE12I/OLVCMOS33Reserved (2)31RE13I/OLVCMOS33Reserved (2)33RE15I/OLVCMOS33Reserved (2)34RE16I/OLVCMOS33Reserved (2)36RE18I/OLVCMOS33Reserved (2)37RE19I/OLVCMOS33Reserved (2)38RE20I/OLVCMOS33Reserved (2)39RE21I/OLVCMOS33Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18 | SDI  |     | LVCMOS33 | SPI Data In. For parameter setting.                           |

| 21         GND          Ground           22         TRGIO         I/O         LVCMOS33         Trigger input/output in synchronous/triggered scrambling mode           23         RE6         I/O         LVCMOS33         Reserved (2)           24         RE7         I/O         LVCMOS33         Reserved (2)           25         UTXD         I/O         LVCMOS33         Reserved (2)           26         RE8         I/O         LVCMOS33         Reserved (2)           27         RE9         I/O         LVCMOS33         Reserved (2)           28         RE10         I/O         LVCMOS33         Reserved (2)           29         RE11         I/O         LVCMOS33         Reserved (2)           30         RE12         I/O         LVCMOS33         Reserved (2)           31         RE13         I/O         LVCMOS33         Reserved (2)           32         RE14         I/O         LVCMOS33         Reserved (2)           33         RE15         I/O         LVCMOS33         Reserved (2)           34         RE16         I/O         LVCMOS33         Reserved (2)           35         RE17         I/O         LVCMOS33                                                                                                         | 19 | GND  | 1   |          |                                                               |

| 22TRGIOI/OLVCMOS33Trigger input/output in synchronous/triggered scrambling mode23RE6I/OLVCMOS33Reserved (2)24RE7I/OLVCMOS33Reserved (2)25UTXDI/OLVCMOS33UART TXD. For parameter setting.26RE8I/OLVCMOS33Reserved (2)27RE9I/OLVCMOS33Reserved (2)28RE10I/OLVCMOS33Reserved (2)29RE11I/OLVCMOS33Reserved (2)30RE12I/OLVCMOS33Reserved (2)31RE13I/OLVCMOS33Reserved (2)32RE14I/OLVCMOS33Reserved (2)33RE15I/OLVCMOS33Reserved (2)34RE16I/OLVCMOS33Reserved (2)35RE17I/OLVCMOS33Reserved (2)36RE18I/OLVCMOS33Reserved (2)37RE19I/OLVCMOS33Reserved (2)38RE20I/OLVCMOS33Reserved (2)39RE21I/OLVCMOS33Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      | 0   | LVCMOS33 |                                                               |

| 23       RE6       I/O       LVCMOS33       Reserved (2)         24       RE7       I/O       LVCMOS33       Reserved (2)         25       UTXD       I/O       LVCMOS33       UART TXD. For parameter setting.         26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33 <t< td=""><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                       |    |      |     |          |                                                               |

| 24       RE7       I/O       LVCMOS33       Reserved (2)         25       UTXD       I/O       LVCMOS33       UART TXD. For parameter setting.         26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         33       RE16       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       <                                                                                                                                                                           |    |      |     |          | Trigger input/output in synchronous/triggered scrambling mode |

| 25       UTXD       I/O       LVCMOS33       UART TXD. For parameter setting.         26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33                                                                                                                                                                                  | 23 | RE6  | I/O |          |                                                               |

| 26       RE8       I/O       LVCMOS33       Reserved (2)         27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                       |    |      |     |          |                                                               |

| 27       RE9       I/O       LVCMOS33       Reserved (2)         28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                        |    |      |     |          | UART TXD. For parameter setting.                              |

| 28       RE10       I/O       LVCMOS33       Reserved (2)         29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      |     |          |                                                               |

| 29       RE11       I/O       LVCMOS33       Reserved (2)         30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |     |          | Reserved (2)                                                  |

| 30       RE12       I/O       LVCMOS33       Reserved (2)         31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28 | RE10 |     |          | Reserved (2)                                                  |

| 31       RE13       I/O       LVCMOS33       Reserved (2)         32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |     |          | Reserved (2)                                                  |

| 32       RE14       I/O       LVCMOS33       Reserved (2)         33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |      |     |          | Reserved (2)                                                  |

| 33       RE15       I/O       LVCMOS33       Reserved (2)         34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      |     |          | Reserved (2)                                                  |

| 34       RE16       I/O       LVCMOS33       Reserved (2)         35       RE17       I/O       LVCMOS33       Reserved (2)         36       RE18       I/O       LVCMOS33       Reserved (2)         37       RE19       I/O       LVCMOS33       Reserved (2)         38       RE20       I/O       LVCMOS33       Reserved (2)         39       RE21       I/O       LVCMOS33       Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32 | RE14 |     |          | Reserved (2)                                                  |

| 35         RE17         I/O         LVCMOS33         Reserved (2)           36         RE18         I/O         LVCMOS33         Reserved (2)           37         RE19         I/O         LVCMOS33         Reserved (2)           38         RE20         I/O         LVCMOS33         Reserved (2)           39         RE21         I/O         LVCMOS33         Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 | RE15 |     |          | Reserved (2)                                                  |

| 36         RE18         I/O         LVCMOS33         Reserved (2)           37         RE19         I/O         LVCMOS33         Reserved (2)           38         RE20         I/O         LVCMOS33         Reserved (2)           39         RE21         I/O         LVCMOS33         Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      |     |          | Reserved (2)                                                  |

| 37         RE19         I/O         LVCMOS33         Reserved (2)           38         RE20         I/O         LVCMOS33         Reserved (2)           39         RE21         I/O         LVCMOS33         Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |     |          | Reserved (2)                                                  |

| 38         RE20         I/O         LVCMOS33         Reserved (2)           39         RE21         I/O         LVCMOS33         Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |     |          | Reserved (2)                                                  |

| 39 RE21 I/O LVCMOS33 Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |     |          | Reserved (2)                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38 | RE20 |     |          | Reserved (2)                                                  |

| 40 RE22 I/O LVCMOS33 Reserved (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |     |          | Reserved (2)                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40 | RE22 | I/O | LVCMOS33 | Reserved (2)                                                  |

(1) Generated by internal voltage regulators.

(2) For possible future use. Connections to I/O pins of a programmable controller are therefore recommended for RE1 to RE8. These I/O pins of the programmable controller should be set to the high-impedance state. (More of RE9 to RE22 may, but need not, be connected to the controller.)

(3) Except for this pin, no external pull-up or pull-down resistors are needed. As far as required, pull-up and pull-down resistors are already implemented on the module.

#### **Power connector**

| Nr. | I/O  |

|-----|------|

| 1   | GND  |

| 2   | +5V  |

| 3   | +5V  |

| 4   | –Fan |

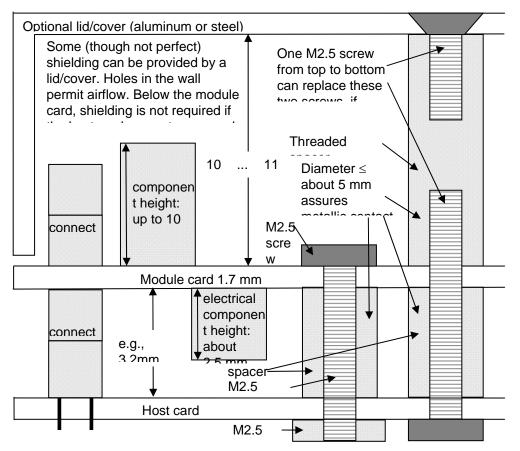

Not needed in an environment where the electrical connector is plugged into a motherboard and cooling airflow is provided.

Recommended if a ribbon cable is used to connect the main electrical connector, in order to reduce ohmic losses. Power is applied at pins 1 and 2. Between pins 4 (negative) and 3 (positive) a 5-V cooling fan with a current of up to 2 A can be connected. It is switched on automatically when the module card needs cooling. With appropriate air ducting, even a 1-W fan is sufficient. A freewheeling diode toward pin 3 (+5V) protects pin 4 (-Fan) against overvoltages during off-switching. A fan is not needed if the user takes otherwise care that the module card stays below +75°C. Normally this is easy, given the low power consumption of the module card.

On the module card there is a reverse polarity protection diode Vishay 12CWQ03F <u>http://www.vishay.com/docs/94132/12cwq03f.pdf</u> (two diode sections connected in parallel). But since

many components on the module card are specified to support only voltages down to -0.3 V one must not at all rely on this! Limiting the maximum supply current can help the module card to survive inadvertedly applied reverse voltage.

#### Serial peripheral interface (SPI)

The module starts operation without SPI. The user doesn't have to use the SPI at all. While the module starts operation without SPI, this serial interface can be used to control function, modify parameters, read back these commands as well as debug register contents.

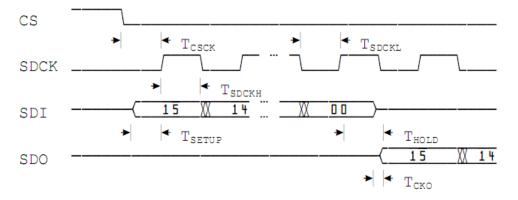

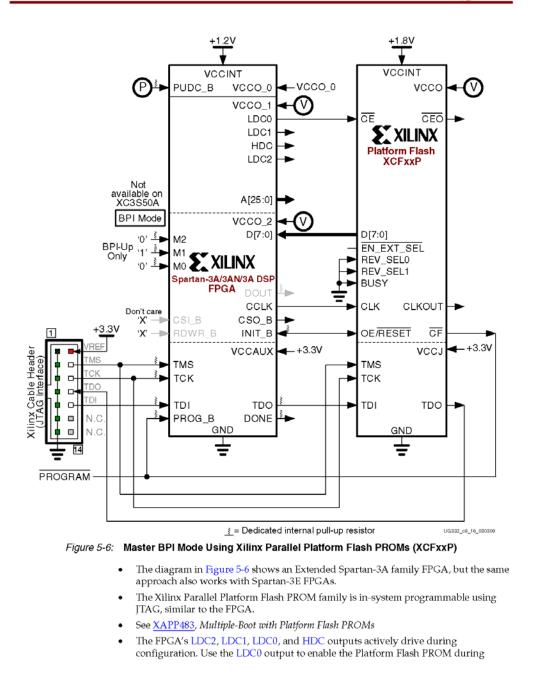

Transmission starts with falling edge of CS and ends with rising edge of CS. After falling edge of CS, the command is transmitted. SDI is sampled with rising edge of SCK. Maximum SCK frequency is 500 kHz. Command and data word length is 16 bit each. MSB of command and data word is sent first, LSB last. If a valid *register read* (RDREG) command is received, the SDO output register shifts with falling edge of SCK to transmit the requested data word. Otherwise SDO remains in high impedance state. Data transfer to the device continues directly after transmitting a *register write* (WRREG) command.

Each SPI register has 16 bit. Upon power-on, all registers are reset to default.

For a possible remote debugging, content of all defined registers needs to be read and sent to Novoptel.

All registers in the 12-bit address space that are not defined below are reserved, and should not be written into!

#### Serial peripheral interface (SPI) commands

| Command | Code  | Data | Function                                       |

|---------|-------|------|------------------------------------------------|

| RDREG   | 0XXXh | OUT  | Read register XXXh (for definition see below)  |

| WRREG   | 1XXXh | IN   | Write register XXXh (for definition see below) |

#### Serial peripheral interface (SPI) registers

| Register<br>address | Bit(s) | Read/<br>Write | Function                                     |

|---------------------|--------|----------------|----------------------------------------------|

| 0                   | 0      | R/W            | HWP rotation enable(1) or disable (0)        |

| 0                   | 1      | R/W            | HWP direction backward(1) or forward(0)      |

| 1                   | 0      | R/W            | QWP0 rotation enable(1) or disable (0)       |

| 1                   | 1      | R/W            | QWP0 direction backward(1) or forward(0)     |

| 2                   | 0      | R/W            | QWP1 rotation enable(1) or disable (0)       |

| 2                   | 1      | R/W            | QWP1 direction backward(1) or forward(0)     |

| 3                   | 0      | R/W            | QWP2 rotation enable(1) or disable (0)       |

| 3                   | 1      | R/W            | QWP2 direction backward(1) or forward(0)     |

| 4                   | 0      | R/W            | QWP3 rotation enable(1) or disable (0)       |

| 4                   | 1      | R/W            | QWP3 direction backward(1) or forward(0)     |

| 5                   | 0      | R/W            | QWP4 rotation enable(1) or disable (0)       |

| 5                   | 1      | R/W            | QWP4 direction backward(1) or forward(0)     |

| 6                   | 0      | R/W            | QWP5 rotation enable(1) or disable (0)       |

| 6                   | 1      | R/W            | QWP5 direction backward(1) or forward(0)     |

| 9                   | 150    | R/W            | HWP rotation speed Bits 150 <sup>(1)</sup>   |

| 10                  | 150    | R/W            | HWP rotation speed Bits 3116 <sup>(1)</sup>  |

| 11                  | 150    | R/W            | QWP0 rotation speed Bits 150 <sup>(2)</sup>  |

| 12                  | 150    | R/W            | QWP0 rotation speed Bits 3116 <sup>(2)</sup> |

| 13                  | 150    | R/W            | QWP1 rotation speed Bits 150 <sup>(2)</sup>  |

| 14                  | 150    | R/W            | QWP1 rotation speed Bits 3116 <sup>(2)</sup> |

| 15                  | 150    | R/W            | QWP2 rotation speed Bits 150 <sup>(2)</sup>  |

| 16                  | 150    | R/W            | QWP2 rotation speed Bits 3116 <sup>(2)</sup> |

| 17                  | 150    | R/W            | QWP3 rotation speed Bits 150 <sup>(2)</sup>  |

| 18                  | 150    | R/W            | QWP3 rotation speed Bits 3116 <sup>(2)</sup> |

| 19                  | 150    | R/W            | QWP4 rotation speed Bits 150 <sup>(2)</sup>  |

| 20                  | 150    | R/W            | QWP4 rotation speed Bits 3116 <sup>(2)</sup> |

| 0.1    | 45.0 | D 44/ | $ONPET (i) = 10^{i}$ (2)                                                    |

|--------|------|-------|-----------------------------------------------------------------------------|

| 21     | 150  | R/W   | QWP5 rotation speed Bits 150 <sup>(2)</sup>                                 |

| 22     | 150  | R/W   | QWP5 rotation speed Bits 3116 <sup>(2)</sup>                                |

| 25     | 150  | R/W   | Optical frequency Index I <sup>(3)</sup>                                    |

| 26     | 150  | R/W   | Current optical frequency band index                                        |

| 27     | 150  | R/W   | Current optical center wavelength                                           |

| 40     | 150  | R/W   | HWP position Index I <sup>(4)</sup>                                         |

| 41     | 150  | R/W   | QWP0 position index I <sup>(4)</sup>                                        |

| 42     | 150  | R/W   | QWP1 position index I <sup>(4)</sup>                                        |

| 43     | 150  | R/W   | QWP2 position index I <sup>(4)</sup>                                        |

| 44     | 150  | R/W   | QWP3 position index I <sup>(4)</sup>                                        |

| 45     | 150  | R/W   | QWP4 position index I <sup>(4)</sup>                                        |

| 46     | 150  | R/W   | QWP5 position index I <sup>(4)</sup>                                        |

| 47     | 150  | R     | Internal table current position dwell time in multiples of 40 ns; Bits 150  |

| 48     | 150  | R     | Internal table current position dwell time in multiples of 40 ns; Bits 3116 |

| 50     | 130  | R/W   | LiNbO <sub>3</sub> section 1 electrode 1 voltage <sup>(5)</sup>             |

| 51     | 130  | R/W   | LiNbO <sub>3</sub> section 1 electrode 2 voltage <sup>(5)</sup>             |

| 52     | 130  | R/W   | LiNbO <sub>3</sub> section 2 electrode 1 voltage <sup>(5)</sup>             |

| 53     | 130  | R/W   | LiNbO <sub>3</sub> section 2 electrode 2 voltage <sup>(5)</sup>             |

| 54     | 130  | R/W   | LiNbO <sub>3</sub> section 3 electrode 1 voltage <sup>(5)</sup>             |

| 55     | 130  | R/W   | LiNbO <sub>3</sub> section 3 electrode 2 voltage <sup>(5)</sup>             |

| 56     | 130  | R/W   | LiNbO <sub>3</sub> section 4 electrode 1 voltage <sup>(5)</sup>             |

| 57     | 130  | R/W   | LiNbO <sub>3</sub> section 4 electrode 2 voltage <sup>(5)</sup>             |

| 58     | 130  | R/W   | LiNbO <sub>3</sub> section 5 electrode 1 voltage <sup>(5)</sup>             |

| 59     | 130  | R/W   | LiNbO <sub>3</sub> section 5 electrode 2 voltage <sup>(5)</sup>             |

| 60     | 130  | R/W   | LiNbO <sub>3</sub> section 6 electrode 1 voltage <sup>(5)</sup>             |

| 61     | 130  | R/W   | LiNbO <sub>3</sub> section 6 electrode 2 voltage <sup>(5)</sup>             |

| 62     | 130  | R/W   | LiNbO <sub>3</sub> section 7 electrode 1 voltage <sup>(5)</sup>             |

| 63     | 130  | R/W   | LiNbO <sub>3</sub> section 7 electrode 2 voltage <sup>(5)</sup>             |

| 64     | 130  | R/W   | LiNbO <sub>3</sub> section 8 electrode 1 voltage <sup>(5)</sup>             |

| 65     | 130  | R/W   | LiNbO <sub>3</sub> section 8 electrode 2 voltage <sup>(5)</sup>             |

| 80     | 130  | R     | Summary of all wave plates rotation enable and direction status             |

| 84     | 150  | R     | Firmware version as 4 digit BCD                                             |

| 85     | 150  | R     | Device DNA word 3 (DNA bits 6348) (same as read via JTAG)                   |

| 86     | 150  | R     | Device DNA word 3 (DNA bits 4732) (same as read via JTAG)                   |

| 87     | 150  | R     | Device DNA word 3 (DNA bits 3116) (same as read via JTAG)                   |

| 88     | 150  | R     | Device DNA word 3 (DNA bits 150) (same as read via JTAG)                    |

| 89     | 150  | R     | LiNbO <sub>3</sub> Device Number (bits $3116$ )                             |

| 90     | 150  | R     | LiNbO <sub>3</sub> Device Number (bits $5110$ )                             |

| 90     | 150  | R     | EPS Unit Serial Number                                                      |

| 96-111 | 150  | R     | Module type code as 32 character string. Beginning at 060h, each Register   |

| 30-111 | 150  | n.    | contains two bytes, representing two ASCII-coded characters.                |

| 123    | 150  | R     | Darc current offset of optional photodetector                               |

| 123    | 150  | R     | Optical power of optional photodetector at upper range limit in $\mu W$     |

| 124    | 150  | R     | Integral part of ADC sample                                                 |

| 128    | 90   | R/W   | Averaging Time Exponent (ATE) for ADC sample                                |

| -      |      |       |                                                                             |

| 130    | 150  | R/W   | Address of internal sampling memory                                         |

| 131    | 150  | R     | Data-Out of internal sampling memory                                        |

| 132    | 0    | R/W   | Timed output enable (1) or disable (0)                                      |

| 133    | 150  | R     | Fractional part of ADC sample, frozen at each reading of register 128       |

| 134    | 150  | R/W   | Maximum memory address for measurements                                     |

| 135    | 150  | R     | Current memory address during measurements                                  |

| 181    | 120  | R     | Current module temperature in °C*2^4                                        |

| 190    | 150  | R     | Number of supported frequency bands                                         |

| 191    | 150  | R     | Center wavelength of frequency band 1                                       |

| 192    | 150  | R     | Maximum frequency in frequency band 1 in THz * 2^7                          |

| 193    | 150  | R     | Minimum frequency in frequency band 1 in THz * 2^7                          |

| 194    | 150  | R     | Maximum frequency index in frequency band 1                                 |

| 195     | 150 | R   | Start frequency index in frequency band 1                                         |

|---------|-----|-----|-----------------------------------------------------------------------------------|

| 195     | 150 | R   | Center wavelength of frequency band 2                                             |

| 190     | 150 | R   | Maximum frequency in frequency band 2 in THz * 2^7                                |

| 198     | 150 | R   | Minimum frequency in frequency band 2 in THz * 2^7                                |

| 199     | 150 | R   | Maximum frequency index in frequency band 2                                       |

| 200     | 150 | R   | Start frequency index in frequency band 2                                         |

| 201-215 | 150 | R   | Reserved for 3 more frequency bands                                               |

| 216     | 150 | R   | Current table row                                                                 |

| 217     | 0   | R   | Indicates a trigger event in the past second                                      |

| 218     | 0   | R/W | Sync mode: Table mode (0) or row mode (1)                                         |

| 219     | 90  | R/W | Table memory address (01023)                                                      |

| 220     | 0   | R/W | Continuous table execution: Disabled (0) or enabled (1)                           |

| 221     | 0   | W   | Table memory write enable. Disabled (0) or enabled (1)                            |

| 222     | 150 | R/W | Table row execution time in multiples of 40 ns; Bits 150                          |

| 223     | 150 | R/W | Table row execution time in multiples of 40 ns; Bits 3116                         |

| 224     | 0   | R/W | External trigger source enable. Disabled (0) or enabled (1)                       |

| 225     | 0   | R/W | Internal trigger source: Periodic counter. Disabled (0) or enabled (1)            |

| 225     | 1   | R/W | Internal trigger source: ATE synchronous. Disabled (0) or enabled (1)             |

| 226     | 0   | R/W | Trigger output enable: Disabled (0) or enabled (1)                                |

| 227     | 0   | W   | Manual trigger event                                                              |

| 228     | 90  | R/W | Table length (01023)                                                              |

| 229     | 0   | R/W | Sync mode enable. Disabled (0) or enabled (1)                                     |

| 230     | 150 | R/W | QWP0 position input for internal table memory                                     |

| 231     | 150 | R/W | QWP1 position input for internal table memory                                     |

| 232     | 150 | R/W | QWP2 position input for internal table memory                                     |

| 233     | 150 | R/W | HWP position input for internal table memory                                      |

| 234     | 150 | R/W | QWP3 position input for internal table memory                                     |

| 235     | 150 | R/W | QWP4 position input for internal table memory                                     |

| 236     | 150 | R/W | QWP5 position input for internal table memory                                     |

| 237     | 150 | R/W | Table row execution time bits 150 input for internal table memory                 |

| 238     | 150 | R/W | Table row execution time bits 3116 input for internal table memory                |

| 240     | 150 | R   | QWP0 position output of internal table memory                                     |

| 241     | 150 | R   | QWP1 position output of internal table memory                                     |

| 242     | 150 | R   | QWP2 position output of internal table memory                                     |

| 243     | 150 | R   | HWP position output of internal table memory                                      |

| 244     | 150 | R   | QWP3 position output of internal table memory                                     |

| 245     | 150 | R   | QWP4 position output of internal table memory                                     |

| 246     | 150 | R   | QWP5 position output of internal table memory                                     |

| 247     | 150 | R   | Table row execution time bits 150 output of internal table memory                 |

| 248     | 150 | R   | Table row execution time bits 3116 output of internal table memory                |

| 250     | 150 | R/W | LiNbO <sub>3</sub> section 1 electrode 1 voltage for internal table memory        |